: 0는 off, 1는 on // Switch

1) 기본적인 논리함수

2) 불 대수의 기본 공식

* 0과 1을 대입해서 옳고 그름을 판단하면 된다

3) 불 대수의 간소화

: 합의 곱, 곱의 합 표현으로 변환한다

: 공통 인수를 뽑아 묶는다

: 법칙 등의 현태로 유도하여 줄여 나간다

4) 카르노 맵(Karnaugh Map) 이용하기

Ex) 논리 함수식 F(A, B, C) = ∑(1, 3, 4, 6)을 간략화 하면?

* 000=0, 001=1, 010=2, 011=3, 100=4, 101=5, 110=6, 111 =7

* https://www.youtube.com/watch?v=jiBtQg84aMY

2. 논리 게이트(기본회로)

: 가장 기본적인 전자소자

: 가장 기본적인 전자소자

* XOR = 두 수가 같으면 0, 다르면 1

* XOR = Exclusive OR gate

* N이 앞에 붙으면 반대의 의미가 되며 기호 끝에 O기호가 붙는다

3. 조합논리회로 : 반가산기

- 조합논리회로

: 임의의 신간에서의 출력이 이전의 입력에는 관계없이 현재의 입력조합으로부터 직접 결정되는 논리회로

: 반가산기, 전가산기, 병렬가산기, 반감산기, 전감산기, 디코더, 인코더, 멀티플렉서, 디멀티플렉서, 다수결회로, 비교기 등

- 반가산기(HA; Half Adder)

: 2진수 두 개를 덧셈한 합(S)과 올림수(C)를 구하는 조합논리회로

- 전가산기(FA; Full Adder)

: 2진수 3자리를 더하여 합(S)과, 올림수(C)를 구하는 회로

: 두 개의 반가산기와 OR가산기

4. 기타 조합논리회로

1. 병렬가산기(PA; Parallel Adder)

: n Bit로 된 2진수 A, B에 대한 덧셈을 n개의 전가산기를 이용해 구현한 실질적인 가산기

: 반가산기, 전가산기, 병렬가산기, 반감산기, 전감산기, 디코더, 인코더, 멀티플렉서, 디멀티플렉서, 다수결회로, 비교기 등

- 반가산기(HA; Half Adder)

: 2진수 두 개를 덧셈한 합(S)과 올림수(C)를 구하는 조합논리회로

- 전가산기(FA; Full Adder)

: 2진수 3자리를 더하여 합(S)과, 올림수(C)를 구하는 회로

: 두 개의 반가산기와 OR가산기

4. 기타 조합논리회로

1. 병렬가산기(PA; Parallel Adder)

: n Bit로 된 2진수 A, B에 대한 덧셈을 n개의 전가산기를 이용해 구현한 실질적인 가산기

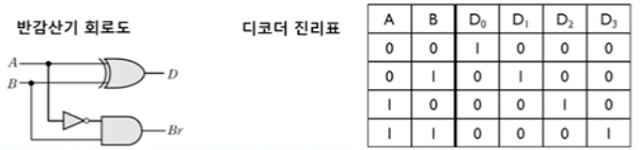

2. 반감산기(HS; Half Subtract)

: 1 Bit 2진수 2자리에 대한 감산을 하는 회로

3. 디코더(Decoder) ~

3. 디코더(Decoder) ~

: n Bit의 정보를 2의n승개의 출력으로 번역하는 회로 (해독기)

: 입력 = n -> 출력 = 2의 n승

4. 인코더(Encoder) ~

: 입력 = n -> 출력 = 2의 n승

4. 인코더(Encoder) ~

: 디코더의 반대 기능 2의n승개의 입력값으로 n개의 출력을 하는 회로

: 입력 = 2의n승 -> 출력 = n

5. 멀티 플렉서(MUX, Multiplexer) ~

: 2의n승의 입력선 중 1개를 선택하여 1개의 출력선으로 출력시키는 회로

: 2의 n승의 입력선 중 1개를 선택 -> 1개를 출력

6. 디멀티플렉서(DeMUX, DeMultiplexer)

: 입력 = 2의n승 -> 출력 = n

5. 멀티 플렉서(MUX, Multiplexer) ~

: 2의n승의 입력선 중 1개를 선택하여 1개의 출력선으로 출력시키는 회로

: 2의 n승의 입력선 중 1개를 선택 -> 1개를 출력

6. 디멀티플렉서(DeMUX, DeMultiplexer)

4. 순서논리회로

: 외부로부터 입력과 현재상태에 따라 출력이 결정되는 회로

: 기억기능이 있다

: 플립플롭과 논리게이트로 구성

: 신호 타이밍에 따라 동기식과 비동기식으로 나누어 진다

: 플립플롭, 카운터, 레지스터, RAM, CPU 등

1) 플립플롭(FF; Flip-Flop)

: 기억기능이 있다

: 플립플롭과 논리게이트로 구성

: 신호 타이밍에 따라 동기식과 비동기식으로 나누어 진다

: 플립플롭, 카운터, 레지스터, RAM, CPU 등

1) 플립플롭(FF; Flip-Flop)

: 전원이 공급되고 있는 한, 상태의 변화를 위한 외부 신호가 발생할 때까지 현재의 상태를 그대로 유지하는 논리회로

: 플립플롭 한 개가 1Bit를 구성하는 2진 셀이다, 1비트를 기억

: 레지스터, RAM, 카운더 등을 구성하는 기본 소자

: 두개의 NAND 또는 NOR게이트를 이용하여 구성

: RS-FF, JK-FF, D-FF, T-FF, RST-FF 등

1-1) RS 플립플롭(Reset-Set FF)

: 플립플롭 한 개가 1Bit를 구성하는 2진 셀이다, 1비트를 기억

: 레지스터, RAM, 카운더 등을 구성하는 기본 소자

: 두개의 NAND 또는 NOR게이트를 이용하여 구성

: RS-FF, JK-FF, D-FF, T-FF, RST-FF 등

1-1) RS 플립플롭(Reset-Set FF)

: 플립플롭의 기본, S와 R선의 입력을 조절하여 임의의 Bit값을 그대로 유지시키거나, 무조건 0 또는 1의 값을 기억시키기 위해서 사용되는 플립플롭

* C = 클럭(외부신호)

* 1은 셋, 0는 리셋

1-2) D 플립플롭

: RS 플립플롭의 R선에 인버터를 추가하여 S선과 하나로 묶어서 입력선을 하나만 구성한 플립플롭

: 해당 값이 그대로 나옴, 그대로 저장하기 위해 사용

1-3) JK플립플롭

: RS-FF에서 S=R=1 일때 동작되지 않는 결점을 보완한 플립플롭

: J=K=1일 경우 보수가 된다(반대)

1-4) T 플립플롭

: JK-FF의 두 입력선을 묶어서 한 개의 입력선으로 구성한 플립플롭

: 현재 상태를 토글(Toggle), 0 = 불변, 1 = 보수

1-5) M/S 플립플롭

: 출력 측의 일부가 입력 측에 궤환되어 유발되는 레이스 현상을 없애기 위해 고안된 FF

* C = 클럭(외부신호)

* 1은 셋, 0는 리셋

1-2) D 플립플롭

: RS 플립플롭의 R선에 인버터를 추가하여 S선과 하나로 묶어서 입력선을 하나만 구성한 플립플롭

: 해당 값이 그대로 나옴, 그대로 저장하기 위해 사용

1-3) JK플립플롭

: RS-FF에서 S=R=1 일때 동작되지 않는 결점을 보완한 플립플롭

: J=K=1일 경우 보수가 된다(반대)

1-4) T 플립플롭

: JK-FF의 두 입력선을 묶어서 한 개의 입력선으로 구성한 플립플롭

: 현재 상태를 토글(Toggle), 0 = 불변, 1 = 보수

1-5) M/S 플립플롭

: 출력 측의 일부가 입력 측에 궤환되어 유발되는 레이스 현상을 없애기 위해 고안된 FF

댓글 없음:

댓글 쓰기